Automating quantum computing laboratory experiments with an agent-based AI framework

Patterns Elsevier (2025) 101372

Abstract:

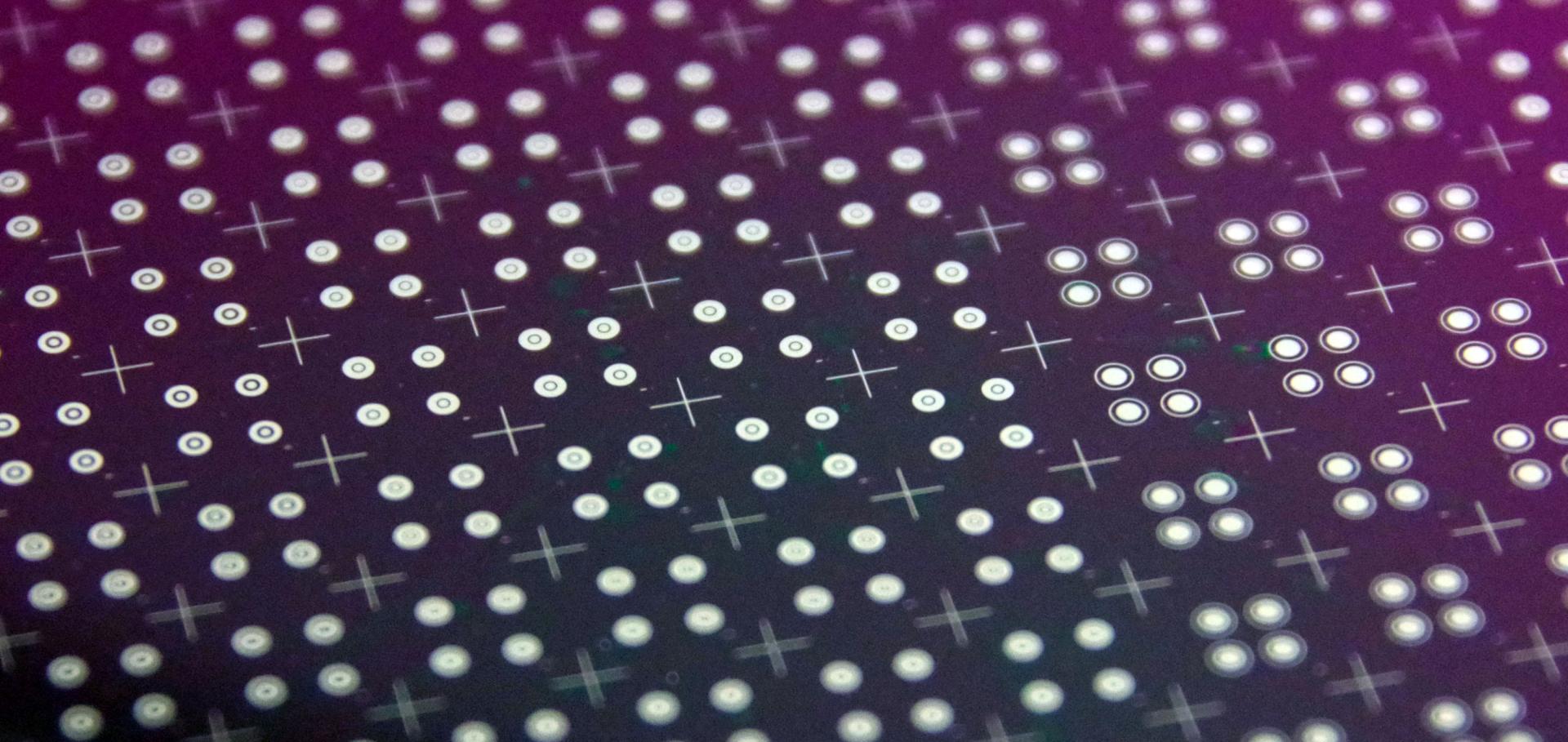

Fully automated self-driving laboratories promise high-throughput, large-scale scientific discovery by reducing repetitive labor. However, they require deep integration of laboratory knowledge, which is often unstructured, multimodal, and hard to incorporate into current AI systems. This paper introduces the “k-agents” framework, designed to support experimentalists in organizing laboratory knowledge and automating experiments with agents. The framework uses large-language-model-based agents to encapsulate laboratory knowledge, including available operations and methods for analyzing results. To automate experiments, execution agents break multistep procedures into agent-based state machines, interact with other agents to execute steps, and analyze results. These results drive state transitions, enabling closed-loop feedback control. We demonstrate the system on a superconducting quantum processor, where agents autonomously planned and executed experiments for hours, successfully producing and characterizing entangled quantum states at human-level performance. Our knowledge-based agent system opens new possibilities for managing laboratory knowledge and accelerating scientific discovery.Efficient Characterization of Qudit Logical Gates with Gate Set Tomography Using an Error-Free Virtual Z Gate Model

Physical Review Letters American Physical Society (APS) 133:12 (2024) 120802

Emulating two qubits with a four-level transmon qudit for variational quantum algorithms

Quantum Science and Technology IOP Publishing 9:3 (2024) 035003

Abstract:

Using quantum systems with more than two levels, or qudits, can scale the computational space of quantum processors more efficiently than using qubits, which may offer an easier physical implementation for larger Hilbert spaces. However, individual qudits may exhibit larger noise, and algorithms designed for qubits require to be recompiled to qudit algorithms for execution. In this work, we implemented a two-qubit emulator using a 4-level superconducting transmon qudit for variational quantum algorithm applications and analyzed its noise model. The major source of error for the variational algorithm was readout misclassification error and amplitude damping. To improve the accuracy of the results, we applied error-mitigation techniques to reduce the effects of the misclassification and qudit decay event. The final predicted energy value is within the range of chemical accuracy.Multi-agent blind quantum computation without universal cluster states

New Journal of Physics IOP Publishing 25:10 (2023) 103028

Abstract:

Blind quantum computation (BQC) protocols enable quantum algorithms to be executed on third-party quantum agents while keeping the data and algorithm confidential. The previous proposals for measurement-based BQC require preparing a highly entangled cluster state. In this paper, we show that such a requirement is not necessary. Our protocol only requires pre-shared Bell pairs between delegated quantum agents, and there is no requirement for any classical or quantum information exchange between agents during the execution. Our proposal requires fewer quantum resources than previous proposals by eliminating the need for a universal cluster state.Low crosstalk in a scalable superconducting quantum lattice

EPJ Quantum Technology Springer Nature (2026)