CaQTuS

The main focus of the CaQTuS project is developing novel ion trap chip architectures for scalable quantum computing. We are particularly interested in developing ion trap chips that combine three specific technologies that favour scalability: quantum charge coupled device (QCCD) architectures, integrated photonics, and microwave quantum logic.

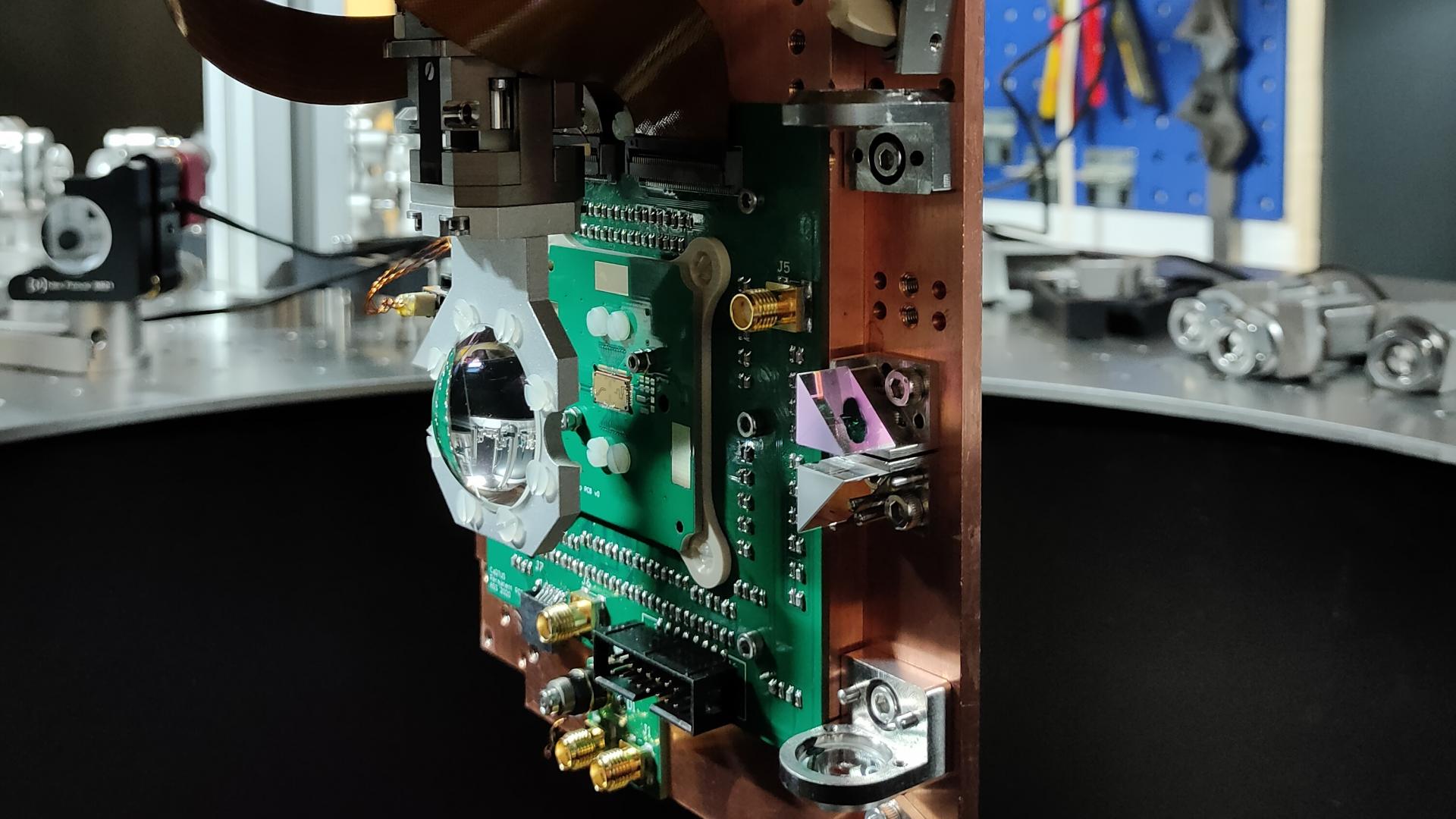

Cold plate of the CaQTuS cryogenic system. In the center of the (green) printed circuit board, you will see a gold ion trapping chip. CaQTuS enables a quick replacement of this chip (on the order of a day) to rapidly test new ion trapping chip architecture.

QCCDs (Nature 417, 709-711; Nature 592, 209-213) utilise the supreme control we can realise over small ion registers, and operate multiple such registers in zones arranged on a two-dimensional grid. Connectivity between the operation zones is then realised through ion shuttling across the chip. One of the challenges of this approach is delivering light to each register. Indeed, parallelizing multiple free-space optical setups for hundreds of ions and ensuring a line of sight to all trapping zones is a daunting task. The use of integrated photonics (Nature 586, 538-542; Nature 586, 533-537) alleviates this problem by integrating beam delivery onto the trap chip itself, and is central to scaling up the size of ion trap chips. Whilst QCCD and integrated photonics have been independently demonstrated, we propose to combine these technologies with microwave-driven quantum logic (Phys. Rev. Lett. 117, 140501; Phys. Rev. Lett. 123, 260503; Nature 597, 209-213). Microwave quantum logic forms a core expertise of the Oxford ion trapping group [COMET] and is expected to facilitate the scaling of ion traps by replacing the most hardware-demanding manipulations of ions – performing logical gates using laser light – by cheaper, smaller, more stable microwave devices driving on-chip components.

In the CaQTuS project, the rapid development of new ion trap architectures is facilitated by a closed-cycle, low-vibration cryogenic system with mechanical design, wiring and optics which are universal with respect to trap design. Operation at cryogenic temperatures (< 10 K) means that we can rely on cryo-pumping to achieve ultra-high vacuum at the ion position, rather than the usual time-consuming cleaning and baking of a vacuum chamber which has historically slowed down progress in the field. Our turnaround time of 24 hours makes CaQTuS a perfect testbed for novel chip architectures.

Research directions

- Designing and testing novel ion trap chip architectures for scalability

- Integrated photonics

- Microwave quantum logic

- Quantum charge-coupled devices

People

Current

- Dr. Chris Ballance (PI)

- Prof. David Lucas (PI)

- Dr. Mario Gely (Postdoc)

- Dr. Koichiro Miyanishi (Postdoc)

- Aaron Leu (Graduate student)

- Molly Smith (Graduate student)

Former

- Ana Sotirova (Masters student)

- Tony He (Summer student)

- Jerry Zheng (Masters student)